# MICROPROCESSOR R www.MPRonline.com THE INSIDER'S GUIDE TO MICROPROCESSOR HARDWARE

# **EMBEDDED PROCESSORS THRIVE IN 2005**

Radical Multicore Chips and Innovative Startup Companies Proliferate By Tom R. Halfhill {1/30/06-02}

Looking back at 2005, we can identify five broad trends in embedded processors. None of these trends actually started last year, but they gained momentum and will be major forces in 2006 and the years to come.

The multicore revolution that broke into the mainstream in 2004 is accelerating. High-performance embedded processors with half a dozen or more processor cores are becoming almost commonplace. Now the attention is expanding to software—particularly the need to create new development tools and techniques for exploiting parallelism.

Startups and new microprocessor architectures keep emerging, undeterred by entrenched competition. Inventors have no shortage of fresh ideas. Fortunately, the investment community has largely recovered from the shock of the 2000 tech bust and is willing to fund new ventures with serious money. Venture capitalists are again prowling our Microprocessor Forums.

More alternatives to designing custom chips keep surfacing, driven by the soaring costs of deep-submicron mask sets and nonrecurring engineering (NRE). A key ingredient in many alternatives is programmable logic. FPGA prices keep falling, steadily altering the equation that determines when programmable-logic devices become more economical than custom ASICs and SoCs. An equally important development is new types of reconfigurable processors that combine programmable logic with fixed logic.

Markets attracting the most attention from chip designers and embedded-system developers are mobile communications, networking, electronic games, digital audio, and digital video. Moreover, the convergence of consumer electronics long anticipated for the living room is now happening in pockets as well. Silicon Valley is gradually losing its status as the unofficial capital of the semiconductor industry. The industry is becoming much more diffuse, due mainly to unprecedented growth in the Asia-Pacific region and India. Companies lacking a multinational strategy or a widely dispersed workforce are often regarded as too small or old-fashioned to compete in world markets. Outsourced engineering is routine. China is becoming more assertive and is destined to become both a world standard-setter and a major developer and exporter of embedded processors.

Following is our analysis of events in 2005 and some speculation about embedded processors in 2006 and beyond. (*Microprocessor Report* broadly defines an embedded processor as any microprocessor not primarily intended to be a CPU for a PC, workstation, or server.) For a concise summary of last year's developments, with links to related *MPR* articles, see the sidebar, "Embedded-Processor Highlights of 2005."

### Land of the Rising Star: China

One of the most interesting events we covered in 2005 was the introduction of China's newest microprocessor, the 64-bit Godson-2. Unfortunately, our exclusive story was widely picked up and bungled by some Internet news sites, which ultimately led the Chinese to clarify their position at a highprofile press conference in Beijing.

As we reported last July, the Chinese developed the Godson-2 for domestic consumption in low-cost PCs and embedded systems. (See *MPR 7/25/05-01*, "China's Emerging

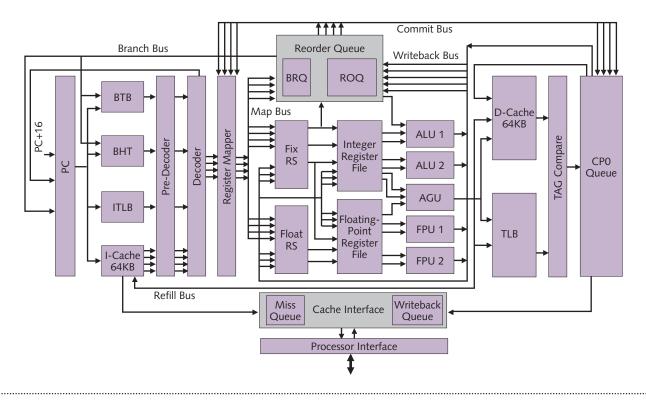

Microprocessors.") Although the Godson-2 is an original microarchitecture, it's patterned after the 64-bit MIPS IV instruction-set architecture (ISA) and bears similarities to the MIPS R10000 server processor introduced by MIPS Technologies in 1995. (See Figure 1.) However, the Godson-2—like the earlier 32-bit Godson-1—isn't truly MIPS compatible. In particular, it won't execute a few instructions patented by MIPS.

*MPR* interviewed the chief architect of the Godson processors, Weiwu Hu, a professor at the Institute of Computing Technology at the Chinese Academy of Sciences in Beijing. Weiwu shared a generous amount of technical information with *MPR*, allowing us to publish the most detailed article about Godson processors to date. He also revealed some of his goals for the future Godson-3, an even more powerful design. It's clear to *MPR* that China has both the engineering talent and the will to design microprocessors as sophisticated as any in the world.

Although the Chinese company responsible for marketing the Godson processors (BLX IC Design Corporation, Ltd.) currently has no plans to sell the chips outside domestic markets, *MPR* believes China will begin exporting original designs by the end of this decade. Obviously, this will have serious ramifications for competitors worldwide. Even before then, independently designed Chinese microprocessors will compete against other chips for sockets inside China, which has now become the world's largest consumer of ICs.

An In-Stat press release about our Godson-2 article inspired widespread coverage of the story in the news media

and on technology-oriented websites. Unfortunately, some writers who never read our article misreported that the Chinese were virtually copying MIPS designs. That struck a nerve with the Chinese, who are often criticized for not respecting intellectual-property (IP) rights. To quell a growing controversy, Weiwu appeared at a press conference in Beijing to deny that he had copied any MIPS designs or infringed on any MIPS patents. At last report, the Chinese were negotiating with MIPS for a license, which would put the matter to rest and allow future Godson processors to be fully compatible with the MIPS architecture.

#### IBM's Cell: Mitosis Has Begun

Another big embedded-processor story of 2005 was the public debut of the Cell Broadband Engine (BE), a radical multicore processor designed by the STI alliance (Sony, Toshiba, and IBM Microelectronics) for the next-generation Sony PlayStation 3 game console. At the International Solid-State Circuits Conference (ISSCC) in San Francisco, the three companies divulged the first technical details about this fascinating chip. *MPR* spent several days interviewing IBM's design engineers, and we analyzed a key U.S. patent filed in 2004. Later, IBM gave a special presentation about the Cell BE at our Spring Processor Forum. (See *MPR 2/14/05-01*, "Cell Moves Into the Limelight," and *MPR 1/3/05-01*, "New Patent Reveals Cell Secrets.")

What emerged from these revelations was an impressive but complex multicore design that seems like overkill

Figure 1. The Chinese Godson-2 processor is roughly similar to the MIPS R10000 and supports most of the MIPS IV ISA, but the microarchitecture is an original design.

for electronic gaming. Indeed, it's now being adapted for other, more serious, applications—such as scientific supercomputing and military weapons.

The first Cell BE integrates a 64-bit Power Architecture (PowerPC) processor core with eight on-chip coprocessors known as synergistic processor elements (SPE). The SPEs are virtually CPUs in their own right, with independent local memories and instruction sets. Instead of using the Power instruction set, they introduce an entirely new set of single-instruction, multiple-data (SIMD) instructions. Technically, the Cell BE is also a multiple-instruction, multiple-data (MIMD) machine, because it simultaneously executes multiple instruction streams. Collectively, the whole thing represents a new architecture that IBM calls the Broadband Processor Architecture (BPA).

Wrapping one's brain around all aspects of Cell is difficult enough, but programming the beast will be even more challenging. IBM is creating new software-development tools and making them available on the web. (See *www.ibm.com/ developerworks/power/cell*.) Because the Cell BE is partly PowerPC-compatible, it may also benefit from any new tools and software spawned by the Power.org Consortium. (See *MPR* 12/27/04-02, "Bringing Power to the People.") One saving grace is that the primary intended market for the Cell BE is the PlayStation 3; videogame programmers are accustomed to odd architectures and experimental development tools.

However, IBM, Sony, and Toshiba are looking far beyond the videogame market. They want to push the Cell BE (or variations of it) into everything from cellphones to supercomputers. That's quite a range. Sony and Toshiba have already committed to using the architecture in consumer electronics, such as high-definition TVs. But IBM will need a lower-power version of the Cell BE and some dynamite development tools to win over the masses of embeddedsystems developers. (See *MPR 2/28/05-01*, "Editorial: Cutting Through Cell's Hype.")

Nevertheless, Cell's potential is too intriguing for some early adopters to pass up. Last June, Mercury Computer Systems became the first company other than IBM's development partners to embrace the architecture. Mercury announced a blade server using Cell BE processors and recently began shipping an evaluation version of a datavisualization system based on the blades. This powerful workstation (see Figure 2) is intended for defense, medical, scientific, and industrial applications.

More recently, Mercury announced a Cell BE "computing appliance" about the size of a toaster. It's designed for mobile computing applications in military vehicles. Another defense contractor, Raytheon, has announced that it will use the Cell BE in missile systems, artillery shells, and radars. And Stanford University is building a Cell BE supercomputer. That a single processor could have so many diverse applications is a testament to the power, versatility, and innovation of the Cell BE design. That's why we gave it our *MPR* Analysts' Choice Award for **Best High-Performance Embedded Processor of 2005.** (See *MPR 1/30/06-01*, "Cell Processor Isn't Just for Games.")

#### More Alternatives to Custom Silicon

ASICs and SoCs reached their glory days in the 1990s, but rising costs are spurring project managers to search for alternatives. FPGAs are satisfactory substitutes in a growing number of embedded systems, as programmable logic rides the cost curve in the direction opposite to custom-designed fixed logic. Every year, the volumes at which FPGAs become more economical than ASICs and SoCs keep changing in favor of programmable logic.

Mindful of this trend, FPGA vendors are making it easier for developers to switch. In 2004, Altera introduced the Nios II, a second-generation 32-bit embedded-processor core optimized for FPGAs. In 2005, archrival Xilinx responded with MicroBlaze v4.00, an improved version of its own 32-bit soft processor. MicroBlaze v4.00 has an optional floatingpoint unit (FPU), a feature missing in Nios II. It also has new pattern-compare instructions, improved debug logic, and higher clock speeds when the core is synthesized for Xilinx's fastest FPGAs. (See *MPR 5/17/05-02*, "MicroBlaze Can Float.")

The most attractive features of both MicroBlaze v4.00 and Nios II are their incredibly low prices. Development kits and licenses cost only \$495—compared with hundreds of thousands or even millions of dollars for other licensable

**Figure 2.** Mercury Computer Systems introduced its Cell Technology Evaluation System (CTES) in January 2006. This powerful workstation is based on the Cell BE blade servers that Mercury announced last June. In addition, Mercury is showing off a compact "computing appliance" for military systems. Meanwhile, Sony and IBM have delivered thousands of Cell BE development systems to PlayStation 3 game programmers.

32-bit processor cores. Altera and Xilinx practically give away their soft processors to encourage sales of FPGAs. As programmable-logic devices gain popularity, *MPR* expects the bargain-basement processors from Altera and Xilinx to exert price pressure on traditional processor-IP vendors, such as ARM, ARC International, MIPS Technologies, and Tensilica.

Altera and Xilinx are the big dogs, but smaller FPGA vendors were active in 2005, too—and they introduced some truly innovative products. Of particular note is Actel, which rolled out the first FPGAs with optimized ARM7TDMI-S processor cores synthesized in programmable logic. (See *MPR 4/4/05-02*, "ARM-Based MCUs Flex Muscles.") This was an important event, because it's the first time ARM has allowed developers to commercially deploy FPGAs with synthesizable ARM cores. (Altera used to sell Excalibur FPGAs with ARM922T processor cores, but those were hard cores implemented in silicon, not soft cores synthesized in the programmable-logic fabric.) Moreover, deploying an Actel FPGA with an ARM core doesn't require buying an ARM license or paying royalties.

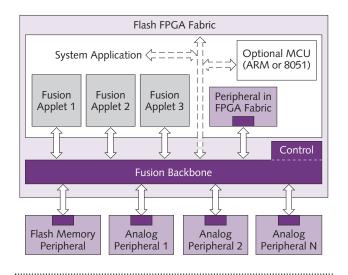

Not content with that accomplishment, Actel introduced a new twist on FPGAs: the Fusion Programmable System Chip architecture (see Figure 3). Essentially, Fusion is a rapid way to develop and deploy SoC designs in programmable logic, with the option of integrating an ARM7TDMI-S or an 8051-compatible processor. (See *MPR 8/15/05-01*, "Actel Mixes Signals on FPGAs.") In December, Actel introduced the first Fusion devices. (See *MPR 12/19/05-02*, "Actel Releases First Fusion Chip.") Any developer looking for an alternative to spinning custom silicon should give Fusion a close look.

Another alternative to custom chips is coming from STMicroelectronics. At the Embedded Systems Conference in March, ST announced a highly integrated chip known as

**Figure 3.** Actel's Fusion integrates analog functions with flash memory and hard or soft IP cores in an FPGA. An ARM7 or 8051 processor core synthesized in programmable logic is optional. An optional AMBA bus and the proprietary Fusion backbone tie everything together.

the STW21000 or V600AT (code-named GreenField). It has an ARM926 hard core, two Ethernet controllers, some additional peripherals, 16Mb of embedded DRAM (eDRAM), and 150,000 gates of programmable logic. Intended primarily for transceivers in wireless base stations, this chip combines the functions of a microcontroller, communications chip, and FPGA. (See *MPR 4/4/05-01*, "ST's Reconfigurable GreenField.")

#### New Consoles Rejuvenate Electronic Games

Microsoft's release of the Xbox 360 just before Christmas signaled a generational turnover of home videogame consoles that will continue in 2006 with the introduction of Sony's PlayStation 3 and Nintendo's Revolution. These consoles have outstanding multimedia capabilities and highspeed networking options. They aren't merely game machines for kids—they're evolving into living-room entertainment centers for the whole family, colliding with Intel's and Microsoft's ambitions for Media Center PCs. Any company lucky enough to land a design win in these consoles is almost guaranteed to ship tens of millions of units.

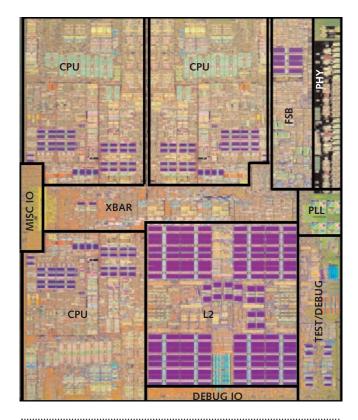

One interesting story of 2005 was the extent to which IBM has become the international arms dealer of video game processors. IBM designed or codesigned CPUs for the three leading vendors of game consoles: Microsoft, Sony, and

**Figure 4.** IBM designed a powerful triple-core processor for Microsoft's Xbox 360 videogame console. The latest PCs are lucky to have dual-core processors. But we're still waiting for IBM or Microsoft to give their game processor an official name.

Nintendo. All three CPUs are based on IBM's Power Architecture (PowerPC to the rest of us), and all three are extreme designs with multiple processor cores. (See Figure 4.) Gone are the days when game consoles could get by with generalpurpose embedded processors or hand-me-down PC chips. (See MPR 10/31/05-01, "IBM Speeds Xbox 360 to Market," and MPR 7/18/05-02, "Powering Next-Gen Game Consoles.")

At the Game Developers Conference last spring, Silicon Valley startup Ageia announced a new chip called PhysX, which Ageia claims to be the first "physics processor" for electronic games. (See *MPR 4/11/05-01*, "Startup Ageia Accelerates Reality.") PhysX is a number-cruncher for simulating virtual environments, which have become considerably more realistic since the days of *Space Invaders* and *Donkey Kong*.

Game consoles aren't the only hot products. Handheld systems like the Nintendo DS and Sony PSP are redefining portable gaming and wireless Internet access for a new generation of users. Youngsters who don't understand or care about the difficult trade-offs between throughput and power consumption are demanding from portable devices the same high quality of experience they expect from tethered systems. Developers have little choice but to keep up.

#### Hot App: Digital Video

Digital video in various forms is showing promise as another killer app. In 2005, Apple introduced the iPod Video, a supplement to Apple's extremely popular line of iPod digital-audio players (14 million sold in 4Q05). At the same time, Apple's iTunes online store began selling downloadable videos starting at \$1.99, jump-starting a new market for video content. Google followed suit in early 2006.

Digital video in the living room is taking off, too. Prices of flat-panel TVs are declining sharply, and HDTV is finally exerting real force in the marketplace. As opportunity knocks, several companies are answering with new processors, processor cores, or processor extensions for accelerating video compression and decompression.

The most notable announcements of interest to developers came from ARC, MIPS, Philips, Tensilica, and Videantis. At Fall Processor Forum 2005, ARC introduced new SIMD extensions for audio/video processing (see *MPR 11/21/05-01*, "ARC Shows SIMD Extensions"), while Tensilica previewed a new video-processor core based on the configurable Xtensa core (see *MPR 11/28/05-01*, "Tensilica Previews Video Engine"). ARC and Tensilica are primarily targeting low-power systems, such as portable video players.

MIPS, which already commands a strong presence in set-top boxes and other video systems, introduced the MIPS32 24KE family of processor cores with new DSP extensions. (See *MPR 5/31/05-01*, "White Paper: The MIPS32 24KE Core Family.") Videantis, a German startup, introduced two synthesizable video decoders based on a common processor core designed especially for video. (See *MPR 11/7/05-01*, "Videantis Chases Digital Video.") With new processors and architectures coming from startups as well as from established companies, the options for licensing digital-video IP will continue expanding in 2006.

Philips Semiconductors, whose parent company (Royal Philips Electronics) is a major consumer-electronics manufacturer, introduced the Nexperia PNX1700, the first chip based on the TriMedia TM5250 processor core. (See *MPR 4/18/05-02*, "Philips Debuts Media Processor.") Philips also announced the first TriMedia core designed for lowpower systems. (See *MPR 12/5/05-01*, "Philips TriMedia Goes Mobile.") Both processors will end up in consumerelectronics products manufactured and sold by Royal Philips Electronics. Although Philips no longer proactively markets TriMedia cores as licensable IP, the cores are still available for licensing and are competitive with rival cores.

As video follows audio out of the living room and into the world at large, there is surging demand for low-power, high-performance video processors in portable systems. And when analog TV gives way to digital TV later in this decade, there will be a huge turnover in consumer video equipment. Clearly, many companies are pursuing these lucrative opportunities, and we expect to see more video processors in 2006.

#### ARM Processors Get Muscular

We've already mentioned some of the year's important events related to licensable processor IP, such as Actel's introduction of the first commercially deployable soft ARM processors in FPGAs; Actel's innovative Fusion chips; ARC's SIMD extensions for digital audio and video; the new MIPS32 24KE family with enhanced DSP extensions; Tensilica's preview of a new audio/video processor; the synthesizable video decoders from German startup Videantis; and the MicroBlaze v4.00 processor from Xilinx. Three other 2005 events were also important to this market.

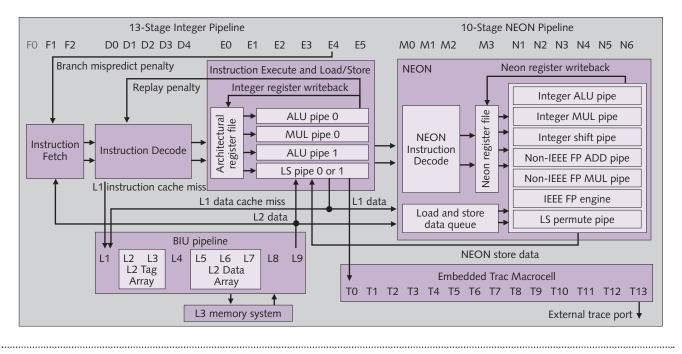

First, ARM introduced its most powerful processor core, the Cortex-A8, code-named Tiger. It's ARM's first superscalar processor, and it's a deeply pipelined machine as well. When coupled with the new Neon media extensions, the Cortex-A8 brings unprecedented performance and clock-frequency headroom to the ARM architecture—without sacrificing too much power efficiency. Indeed, ARM designed the Cortex-A8 for next-generation cellphones, which must deliver rich media content while coolly operating on small batteries in a tiny package. At least five key licensees are already working with the Cortex-A8. (See our detailed twopart coverage in *MPR 10/25/05-02* and *MPR 11/14/05-01*, "Cortex-A8: High Speed, Low Power.")

As Figure 5 shows, the Cortex-A8 is a sophisticated processor with a 13-stage integer pipeline, floating-point hardware, multiple levels of cache, and Neon media extensions. Because of its power-efficient design and strategic significance, we are giving the Cortext-A8 our *MPR* Analysts' Choice Award for **Best Processor-IP Core of 2005**. (See *MPR 1/30/06-07*, "Cortex-A8 Balances Power, Performance.")

At Spring Processor Forum 2005, ARM licensee Marvell announced a new ARM-compatible processor called Feroceon.

5

6

Figure 5. The Cortex-A8 is a far cry from the ARM7, ARM's most popular processor core. While the ARM7 has a simple three-stage pipeline and no caches, the Cortex-A8 microarchitecture more closely resembles that of a PC processor.

It's a standard-part chip built around a hard core, not a licensable soft core, which would seem to make it irrelevant in this discussion of licensable IP. However, Feroceon advances the ARM architecture in much the same way as the Cortex-A8 does. Feroceon is the first ARM-architecture processor with out-of-order execution, as well as other high-performance features. Those improvements should allow Feroceon to

| Memory<br>Controller 1                  | Bridge  |       | XGMII and SPI-4.2      |

|-----------------------------------------|---------|-------|------------------------|

| L2 Bank 8                               |         | CPU 8 | Port 1                 |

| L2 Bank 7                               | ect     | CPU 7 |                        |

| L2 Bank 6                               | erconn  | CPU 6 | ndorie un Standard     |

| L2 Bank 5                               | ed Inte | CPU 5 | 원 Security<br>없 Accel. |

| L2 Bank 4                               |         | CPU 4 | Engine                 |

| L2 Bank 3                               |         | CPU 3 |                        |

| L2 Bank 2                               | Vemo    | CPU 2 | GMAC 0:3               |

| L2 Bank 1                               |         | CPU 1 | Port 0                 |

| Memory<br>Controller 0<br>QDR SRAM/LA-1 |         |       |                        |

**Figure 6.** Packing eight multithreading processors on a 15.3mm  $\times$  14.8mm die (when fabricated at 90nm) required some tight floorplanning by RMI's design team. This 333-million-transistor chip booted a 32-way Linux OS within three days after RMI received the first silicon.

deliver considerably more throughput than developers have come to expect from an ARM-based chip. In fact, Feroceon may deliver enough throughput to compete with MIPS and PowerPC processors in higher-end networking and communications applications—new markets for ARM. (See *MPR* 5/23/05-01, "Marvell Puts ARM Out of Order.")

The third important IP-related event of 2005 was a U.S. patent on the fundamental technology of configurable processors. ARC won the patent, though not without some dickering with the patent office, which required modifications to the original claims. Nevertheless, it's a key patent on important technology, and it could affect companies beyond ARC's direct competitors. The patent could also set up a showdown with one competitor, Tensilica, although that company received equally good news from the patent office at around the same time. (See our detailed analysis in *MPR 8/29/05-01*, "ARC Patent Looks Formidable.")

#### Network Processors Make a Comeback

In 2006, wireless networking will finally come of age. This will probably be the watershed year when consumers expect almost all portable electronics devices—such as notebook computers, PDAs, cellphones, and game machines—to incorporate some form of wireless networking or Internet access. You'll know the tide has turned when Apple blesses the world with an iPod capable of downloading music and video directly from the iTunes website, without detouring through a computer.

Network infrastructures provide an almost limitless opportunity for embedded processors. In the past, network expansion was all about adding capacity. Now it's about

#### Embedded-Processor Highlights of 2005

Actel introduced the first FPGAs with specially optimized ARM7TDMI-S processor cores embedded in programmble logic (see *MPR 4/4/05-02*, "ARM-Based MCUs Flex Muscles"), then followed by announcing its Fusion Programmable System Chip (PSC) architecture. (See *MPR 8/15/05-01*, "Actel Mixes Signals on FPGAs.") As the year drew to a close, Actel introduced the first Fusion devices. (See *MPR 12/19/05-02*, "Actel Releases First Fusion Chip.")

**Ageia**, a Silicon Valley startup, surfaced at the Game Developers Conference to show off its PhysX chip, billed as the world's first "physics processor" for electronic games. (See *MPR 4/11/05-01*, "Startup Ageia Accelerates Reality.")

ARC International released six synthesizable processor cores based on the existing ARC 600 and ARC 700. (See *MPR* 3/14/05-02, "ARC's Preconfigured Cores."). On March 1, ARC won a significant U.S. patent for its configurable-processor technology. (See *MPR* 8/29/05-01, "ARC Patent Looks Formidable.") At Spring Processor Forum, ARC introduced new floating-point extensions for its processor cores. (See *MPR* 5/23/05-02, "Float Without Bloat."). At Fall Processor Forum, ARC introduced new single-instruction, multipledata (SIMD) extensions for digital audio/video processing. (See *MPR* 11/21/05-01, "ARC Shows SIMD Extensions.")

**ARM** took the stage at Fall Processor Forum to reveal the first technical details about its first superscalar processor core, the Cortex-A8. (See our two-part coverage in *MPR* 10/25/05-02 and *MPR* 11/14/05-01, "Cortex-A8: High Speed, Low Power.") Earlier in the year, ARM introduced Jazelle RCT (Run-time Compilation Target), new Thumb-2EE extensions for reducing code bloat when compiling Java bytecode into native code. (See *MPR* 7/11/05-01, "ARM Strengthens Java Compilers.")

**Broadcom** won our *MPR* Analysts' Choice Award for the Best High-Performance Embedded Processor of 2004: the quad-core BCM1480. (See *MPR* 1/31/05-02, "Multicore Chips Rule in 2004.")

**Cambridge Consultants**, a British engineering firm, appeared at Spring Processor Forum to introduce its first licensable 32-bit embedded-processor core, the XAP3. (See *MPR 6/13/05-01*, "XAP3 Takes the Stage.")

**Cavium Networks** introduced two secure communications processors for small-office/home-office applications (see *MPR 2/7/05-01*, "Cavium Expands Security") and later announced the new Octeon EXP family of multicore network processors, which omit the integrated security engine found in the Octeon NSP family (see *MPR 9/6/05-01*, "Cavium: Security Optional").

**China** took an important step onto the world stage by introducing the Godson-2, a new 64-bit microprocessor patterned after the MIPS IV instruction-set architecture (albeit

without a MIPS license). *Microprocessor Report* interviewed the chief architect of the Godson processors. (See *MPR* 7/25/05-01, "China's Emerging Microprocessors.")

**EEMBC**, the Embedded Microprocessor Benchmark Consortium, released the new Digital Entertainment benchmark suite. (See *MPR 2/22/05-01*, "EEMBC Expands Benchmarks.")

**Elixent** used Spring Processor Forum to introduce a better version of the on-chip network fabric in its massively parallel configurable-processor core. (See *MPR 6/27/05-02*, "Elixent Improves D-Fabrix.")

**Freescale Semiconductor** introduced two new chips in the PowerQUICC II Pro family (see *MPR 3/21/05-01*, "Freescale Quickens PowerQUICC") and set a new EEMBC speed record with the PowerPC MPC7448, a high-performance embedded processor. (See *MPR 7/5/05-01*, "PowerPC Ain't Dead Yet.")

**IBM Microelectronics**, **Sony**, and **Toshiba** made noise at ISSCC by revealing the first significant technical details about the Cell Broadband Engine processor for the Sony PlayStation 3. (See *MPR 2/14/05-01*, "Cell Moves Into the Limelight.") A few months later, IBM disclosed details about its multicore processor for the new Microsoft Xbox 360. (See *MPR 10/31/05-01*, "IBM Speeds Xbox 360 to Market," and *MPR 7/18/05-02*, "Powering Next-Gen Game Consoles.")

Infrant Technologies, a four-year-old California-based company, introduced a new RAID controller based on the freely licensable SPARC-compatible LEON processor core. (See *MPR 5/2/05-02*, "Storage Processor Leverages LEON.")

**Innovative Silicon** impressed attendees at Fall Processor Forum with a new embedded-memory technology that has one transistor per bit-cell, like DRAM, but doesn't need a deep-trench capacitor. (See *MPR 10/25/05-03*, "Z-RAM Shrinks Embedded Memory.")

**Intrinsity** withdrew from the fabless-semiconductor market and adopted a new business model of licensing its innovative Fast14 logic and development tools as intellectual property. (See *MPR 1/10/05-02*, "Intrinsity Takes Its IP on the Road.")

Luxtera, a California-based startup, announced new technology for integrating optical communications components on traditional silicon wafers without using exotic materials. (See *MPR* 7/25/05-02, "Luxtera: Photonic Revolutionary.")

**Marvell** used Spring Processor Forum to unveil a high-performance ARM-compatible processor, Feroceon, that brings out-of-order execution to the ARM architecture for the first time. (See *MPR 5/23/05-01*, "Marvell Puts ARM Out of Order.")

**Matsushita** gave a presentation at Spring Processor Forum revealing a scalable approach to media processing.

7

8

# Embedded-Processor Highlights of 2005 Continued

It's oriented around two highly integrated SoCs: the Instruction Parallel Processor and the Data Parallel Processor. (See *MPR 6/20/05-02*, "Matsushita's Own Media Platform.")

**MIPS Technologies** introduced the MIPS32 24KE family of licensable embedded-processor cores at Spring Processor Forum—adding DSP extensions to the existing MIPS32 24K family. (See *MPR 5/31/05-01*, "White Paper: The MIPS32 24KE Core Family.")

**NEC's Mobile System Division** appeared at our first Microprocessor Forum Japan to present the MP211, a parallelprocessing SoC with three ARM926 cores for handheld communications devices. (See *MPR* 12/27/05-01, "MP Cores for Handheld Apps.")

**Oki Semiconductor** unveiled the world's smallest ARM-based microcontrollers. (See *MPR 4/4/05-02*, "ARM-Based MCUs Flex Muscles.")

**P.A. Semi** made its public debut at Fall Processor Forum to announce the PowerPC-based PWRficient multicore processor. (See *MPR 10/25/05-01*, "P.A. Semi: New Blood for Power.")

**Philips Semiconductors** announced the first ARM9based microcontrollers fabricated in a 90nm CMOS process (see *MPR 4/4/05-02*, "ARM-Based MCUs Flex Muscles") and introduced the Nexperia PNX1700, the first chip based on the Tri/Media TM5250 processor core. (See *MPR 4/18/05-02*, "Philips Debuts Media Processor.") Later in the year, Philips introduced a new line of low-price ARM7-based microcontrollers (see *MPR 10/10/05-01*, "Philips Challenges 8-Bit MCUs") and announced the first Tri/Media processor core for low-power applications. (See *MPR 12/5/05-01*, "Philips Tri/Media Goes Mobile.") **Raza Microelectronics** emerged from stealth mode at Spring Processor Forum to announce its XLR family of networking processors, which will have as many as eight multithreaded MIPS64-compatible processor cores. (See *MPR 5*/17/05-01, "A New MIPS Powerhouse Arrives.")

Silicon Hive appeared at Spring Processor Forum to introduce two new processor cores based on its unique ultralong instruction word (ULIW) architecture. (See *MPR* 6/20/05-01, "Busy Bees at Silicon Hive.")

**STMicroelectronics** announced a chip variously known as the STW21000, the V600AT, and GreenField. It integrates an ARM926 core with reprogrammable logic and peripherals, mainly for wireless base stations. (See *MPR* 4/4/05-01, "ST's Reconfigurable GreenField.")

**Tensilica** won our *MPR* Analysts' Choice Award for the Best IP-Core Processor of 2004: Xtensa LX. (See *MPR 1/24/05-01*, "Best Processor Cores of 2004.") At Fall Processor Forum 2005, Tensilica gave attendees an early look at a new licensable video-decoder engine and announced a new version of its Xtensa configurable-processor core. (See *MPR 11/28/05-01*, "Tensilica Previews Video Engine" and the sidebar, "Tensilica Introduces Xtensa 6 Processor Core.")

**Videantis**, a German startup, introduced two licensable video-processing modules at Fall Processor Forum one for low-power mobile applications and the other for high-performance digital TVs. (See *MPR* 11/7/05-01, "Videantis Chases Digital Video.")

Xilinx appeared at Spring Processor Forum to announce an optional FPU for its licensable 32-bit processor core, the MicroBlaze v4.00. (See *MPR 5/17/05-02*, "MicroBlaze Can Float.")

adding capability, too. Cryptography, security filtering, and prioritized traffic management consume as much processing power as designers can deliver, especially as wire speeds keep increasing. It's no coincidence that a rising star in this market is Cavium Networks. Cavium made a strong debut in 2002 with security processors and is rapidly introducing new families of multifunction chips integrating as many as 16 MIPS64-compatible processor cores. (See *MPR 2/7/05-01*, "Cavium Expands Security," and *MPR 9/6/05-01*, "Cavium: Security Optional.")

Two much-anticipated startups formerly operating in stealth mode became debutantes in 2005: Raza Microelectronics (RMI) and P.A. Semi. Thanks to experienced founders, both companies seem more like veterans than newcomers. RMI, founded by former AMD and NexGen executive Atiq Raza, appeared at Spring Processor Forum 2005 to announce its XLR network processors, which integrate as many as eight multithreaded MIPS64-compatible processor cores on a single chip. In concept, XLR is similar to Sun Microsystems' Niagara server processors, which also rely on both multithreading and multiprocessing for greater efficiency. But RMI is gunning for routers and other network equipment, where packet processing breaks down more easily into parallel threads. (See *MPR 5/17/05-01*, "A New MIPS Powerhouse Arrives")

P.A. Semi has star power, too. Founders include Dan Dobberpuhl, Jim Keller, and Peter Bannon, some of the wizards behind the commercially unsuccessful but technically impressive DEC Alpha. P.A. Semi took the stage at Fall Processor Forum 2005 to announce a dual-core chip, the PowerPC-based PWRficient processor. (See *MPR 10/25/05-01*, "P.A. Semi: New Blood for Power.") Displaying bravado reminiscent of IBM's ambitions for the Cell architecture, P.A. Semi insists that the PWRficient processor isn't just for networking. It's intended to be a general-purpose processor for a variety of high-performance applications, such as settop boxes, printers, storage systems, servers—and, perhaps, future game consoles. PWRficient chips will debut next year in a 65nm fabrication process.

One company that sounds like a newcomer but is really a veteran is Freescale Semiconductor, which was liberated from Motorola in 2004. Freescale has been overhauling its extensive PowerQUICC line with improved PowerPC cores, newly integrated security engines, faster I/O interfaces, and better programmability for the on-chip auxiliary processors. (See *MPR 3/21/05-01*, "Freescale Quickens PowerQUICC.") With hungry new competitors like Cavium, Marvell, P.A. Semi, and RMI entering the chase, that's a smart thing to do.

Freescale isn't ignoring its less integrated standalone processors. In 2005, the new 1.7GHz MPC7448 set a speed record with the EEMBC benchmarks, making it the world's fastest high-performance embedded processor. (See *MPR* 7/5/05-01, "PowerPC Ain't Dead Yet.") We expect Freescale to continue refining the PowerQUICC line in 2006 and to migrate more designs to 90nm.

We don't expect Freescale to suffer much from Apple's recent switch to Intel processors in Macintosh computers. Although Freescale has been supplying PowerPC G4 processors for Apple's PowerBooks and iBooks, the volumes apparently didn't justify developing new processors specifically for Apple, and the G4 is nearing the end of its useful life as a notebook processor, anyway. Apple's source for desktop Power-PC processors is IBM, which seems even less worried than Freescale about Apple's defection. Now it is Intel's turn to deal with Apple's low-ball price negotiations—a classic case of irresistible force meeting immovable object.

#### Wireless Technology Brightens the Future

The outlook for network and communications processors looks stronger than it's been since the tech bust of 2000, especially as wireless networking spreads its wings. *MPR* expects wireless technology to create significant demand for embedded processors over the next several years. Wireless will drive demand for low-power processors in clients and for high-performance processors in base stations and other parts of the infrastructure. Numerous products that today aren't considered communications devices will gain the ability to communicate wirelessly.

Wireless technology will soar at the end of this decade when analog TV broadcasting goes off the air and is replaced by digital TV. The U.S. government will auction off large swaths of radio-frequency spectrum now hogged by analog TV channels, creating opportunities for new kinds of wireless services. And because the analog channels occupy lower-frequency parts of the radio spectrum, the new services will enjoy wider coverage and greater penetration through buildings and other obstacles than the higher-frequency bands now used by wireless standards like Wi-Fi.

By then, consumers will expect wireless connectivity in almost every electronic product. Mobility will be ubiquitous. The challenge for developers will be to pack all the features that consumers demand into small, efficient, battery-powered systems. New battery technologies like miniature fuel cells might relieve some pressure, but the diminishing returns and rising costs of process shrinks will cause headaches and long working hours for many engineers struggling to design power-efficient systems.

## To subscribe to Microprocessor Report, phone 480.483.4441 or visit www.MPRonline.com

© IN-STAT